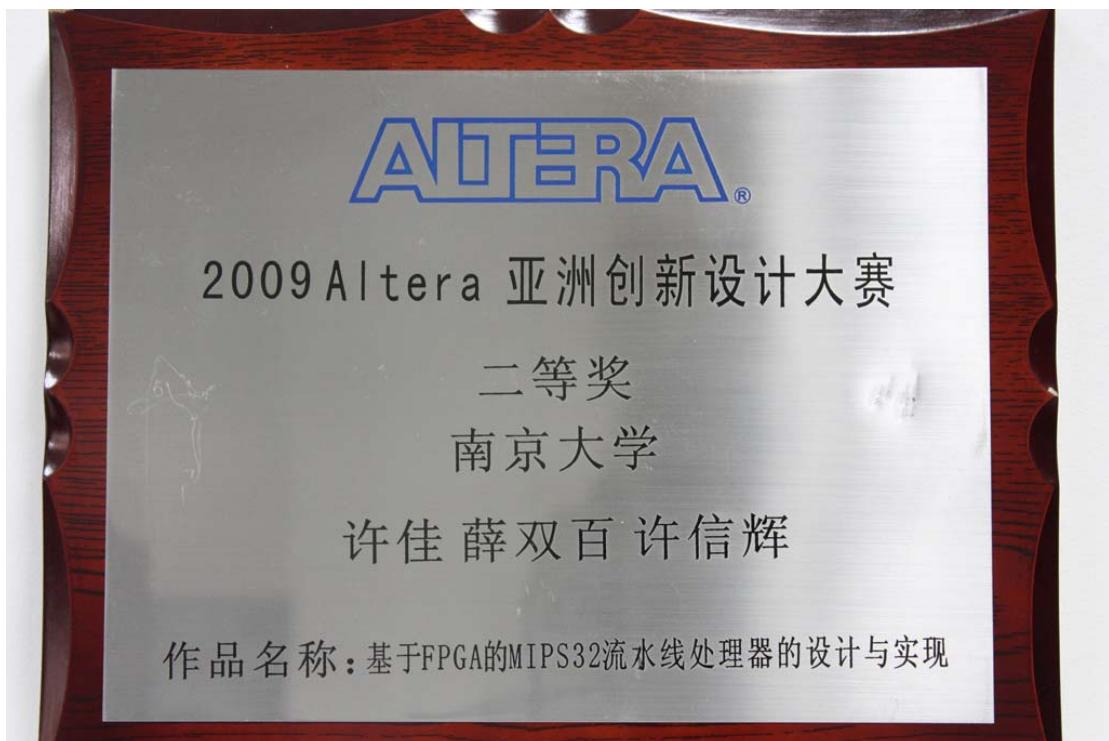

喜讯：我系本科生创新团队 MIPS 处理器设计项目荣获

Altera 2009 亚洲创新大赛二等奖

我系本科生薛双百、许佳、许信辉组成的创新团队在由美国 Altera 公司举办的 2009 亚洲创新设计大赛中以“基于 FPGA 的 MIPS32 流水线处理器的设计与实现”的参赛项目，经过激烈角逐，于 10 月 16 日荣获大赛 2 等奖。

Altera 2009 亚洲创新大赛由美国 Altera 公司发起和组织。Altera 公司是全世界在可编程逻辑(FPGA)技术领域的领导企业；该大赛是亚太区最高荣誉的 FPGA 设计竞赛，水平高，影响大，今年已经是连续第六届，参赛者为大学在读的研究生和本科生。

本次大赛参赛队伍众多，有来自全国的 630 多支队伍参赛，其中大多数是研究生组成的参赛队伍。按照大赛指导原则，各参赛项目必须契合 Altera 公司的目标应用市场，设计项目必须具有创新性和实用性，并且具有较高的设计水平和难度。参赛项目覆盖了航空、汽车、便携式、工业、家用电器、医疗、无线通信、计算机等诸多应用领域。参赛项目不仅水平高，而且具有很明确的应用目标，绝大多数项目都带着完成的设备和系统实物参赛。大赛竞争激烈，评审严格，且持续时间长。从今年 4 月开始，大赛经过了初赛、复赛和决赛 3 轮、历时 6 个月的过程。

由本系本科生薛双百、许佳、许信辉组成的创新团队，在相关指导老师指导下，在他们去年“计算机组成原理”课程实践项目所完成的 20 多条指令的原型 MIPS 流水线处理器的基础上，勇于挑战，大胆创新，在 Altera DE2-70 开发平台上，基于 FPGA 设计实现了兼容于 MIPS32 Revision 2.62 工业标准的 5 段流水线 MIPS32 处理器，完成了一个大胆而具有很大技术挑战的创新设计。

该 MIPS32 处理器用 Verilog 硬件描述语言设计完成，设计实现了 80 多条指令，覆盖了除浮点运算以外的绝大多数指令；处理器具有流水线数据转发和冒险检测能力，能检测和处理流水线中的各种冒险和冲突；在 CP0 协处理器中实现了中断和异常处理；集成并兼容于 Wishbone 工业标准总线；此外，为了进行调试和测试，还实现和集成了存储器和串行输入/输出接口。设计完成的处理器在通过了时序分析和验证后，下载到 FPGA 芯片中进行了实际的运行和验证测试，通过运行小应用程序完成了最终的功能测试。经过初步分析和比较，除尚未实现的浮点运算功能外，该处理器在计算能力和性能上接近于“龙芯”初期（2001 年）所完成的原型 MIPS 处理器的水平。

经过前两轮的激烈角逐，该项目最后从数百支参赛队伍中脱颖而出，闯进了前 28 强，于 9 月 22 日顺利进入决赛，并于 10 月 12 日赴上海参加了现场的决赛答辩和演示。在答辩和演示过程中，Altera 公司的专家评委对本队同学进行了非常深入和刁钻的技术提问和考核，甚至查看了项目的工程文件和代码，最后，评委为本队同学的出色工作和完美表现所折服。经过激烈角逐和严格评比，最后本项目在 28 个决赛项目、630 多个全部参赛项目中位列第 5，荣获 2 等奖。

本参赛项目的成功大大拓宽了 Altera 开发平台在“计算机组成原理”、“微机接口技术”、“嵌入式系统”等计算机专业相关课程实验教学中的应用，为在国内高校计算机专业实验教学和研究中进行基于 FPGA 的软核处理器（如嵌入式 SOC, GPU, DSP 等）设计起到了很好的示范作用。

同时，本参赛项目的工作也体现了本系优秀学生具有较强的计算机系统设计的实践能力；也体现了计算机组成原理等相关课程的理论和实践教学取得了较好的教学效果。

该创新团队目前还在继续进行更多处理器功能的研究开发工作，计划实现浮点运算部件、存储器管理部件(虚拟存储器和 cache)，转移指令分支预测和总线扩展。该工作将成为相关课程实践教学研究的一个良好的基础；后续我们将安排更多本科生和研究生在此基础上进行进一步的研究开发工作，如设计多核处理器，开发运行于该处理器的原型操作系统、编译程序以及应用程序等，期望探索并提供一种理论联系实际、融会贯通计算机软硬件系统的理论和实践教学模式。